Alles begann 1975 mit dem 6501, der von der Firma MOS Technologies entwickelt wurde, um dem 6800 von Motorola möglichst ähnlich zu sein. MOS Technologies bestand aus ehemaligen Motorola-Mitarbeitern, darunter der Gründer der Firma und späterer Entwickler des Commodore PET, Chuck Peddle. Da der 6501 praktisch dem 6800 entsprach, aber nur einen Bruchteil kostete, drohte Motorola mit einer Klage. Als Folge entwickelte MOS den 6502.

Der technische Hauptunterschied zwischen dem 6502 und dem 6800 war, dass der 6800 einen externen Taktgenerator brauchte, der 6502 diesen aber bereits integriert hatte. Außerdem war der 6502 nicht mehr pinkompatibel zum 6800. Jetzt konnte Motorola nichts mehr einwenden, und trotzdem konnten Programmierer, die sich mit dem 6800 auskannten, sich schnell auf den 6502 umgewöhnen, da der Befehlssatz sehr ähnlich war. Der größte Unterschied aber war der Preis, nämlich 175 $ für den 6800 und nur 25$ für den 6502. Dies war mit der Grund, dass für den Apple 1 und II diese CPU gewählt wurde, obwohl der Apple 1 sowohl mit 6502 als auch mit 6800 bestellt werden konnte.

Vorgestellt wurde der Prozessor mit dem legendären Selbstbaukit namens KIM-1, der ebenfalls von MOS Technologies stammte. Der 6502 wurde in fast allem wo Commodore draufstand verwendet, sogar im Amiga (der Tastaturcontroller war ein modifizierter 6502).

Die Technik

Im Unterschied zu den Intel 8080 CPUs hatte der 6502 sehr wenige Register. Er war ein 8 Bit-Prozessor, mit 16 Bit Adressbus. Zu dieser Zeit war der Arbeitsspeicher schneller als eine CPU, also machte es Sinn ,die CPU für Speicherzugriffe zu optimieren. Eingebaut waren ein 8 Bit Datenregister, zwei 8 Bit Indexregister und ein 8 Bit Stapelzeiger (der Stapelspeicher ging von Adresse 256 ($100 hex) bis 511 ($1ff). Der Prozessor benutzte diese Register sehr effektiv und besaß mehrere Adressierungsmodi. Einer davon war der Zero-page Modus, der die Speicheradressen 0 - 255 mit einer 8-bit Adresse ansprechen konnte, was die Abarbeitung beschleunigte (der Prozessor musste das zweite Byte der Adresse nicht einlesen).

Die 650x Familie benutzte das Little-Endian Format, bei dem das niederwertige Byte vor dem höherwertigen gespeichert wird. So wird aus der Adresse $1234 im Speicher $34 $12. Der Vorteil war, dass das niedrigere Adressbyte zu einem Index-Register addiert werden konnte , während das obere Byte noch geholt wurde.

Modellübersicht der 6502-Familie

Wie bei den 6800 wurden Varianten der CPU produziert, die sich zum Beispiel in zusätzlichen I/O-Ports, mehr Adressbereich (oder auch weniger, um Kosten zu sparen) zeigten. Alle Modelle mit dem Nummernschema XX0X besitzen eine Taktgenerator auf dem Chip, bei den Modellen mit dem Schema XX1X wird die Taktung extern geregelt. Von den meisten Modellen (bis zum 6505 bzw. 6515) gibt es beide Versionen.

| Modell | Adressbus | Gehäuse | Besonderes | Verwendet in |

|---|---|---|---|---|

| 6502 / 6512 | 16 Bit | 40 Pin | Basisversion | PET-Serie, VIC20, VIC 1540, VIC 1541, CBM 2040-Serie |

| 6502A | 16 Bit | 40 Pin | Beschleunigte Version des 6502 | |

| 6502B | 16 Bit | 40 Pin | Beschleunigte Version des 6502, zugelassen bis ~3 Mhz | |

| 65C02 | ? | ? | 16-Bit Version des 6502. Neue Instruktionen und zwei neue Adressierungsmodi | |

| 6503 / 6513 | 12 Bit | 28 Pin | ||

| 6504 / 6514 | 13 Bit | 28 Pin | CBM 2040 | |

| 6505 / 6515 | 12 Bit | 28 Pin | ||

| 6506 | 12 Bit | 28 Pin | ||

| 6507 | 13 Bit | 28 Pin | Besitzt keine Interrupts | |

| 6509 | 20 Bit | 40 Pin | CBM-II Serie | |

| 6510 | 16 Bit | 40 Pin | Besitzt einen zusätzlichen 6-Bit Datenport | C64 |

| 7501 | 16 Bit | 40 Pin | 6502 in HMOS-I-Technologie. | plus/4-Serie |

| 8500 | 16 Bit | 40 Pin | 6510 in CMOS-Technologie. | C64c |

| 8501 | 16 Bit | 40 Pin | 7501 in HMOS-II-Technologie. | plus/4-Serie |

| 8502 | 16 Bit | 40 Pin | 6510 umschaltbar auf 2 Mhz | C128 |

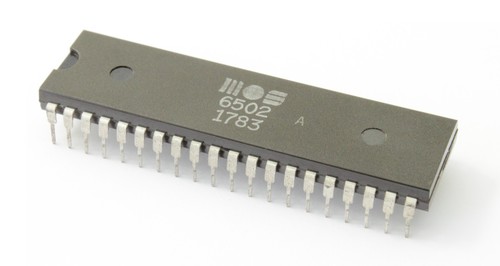

| Datenblatt: | MOS Technologies 6502 |

|---|---|

| Erscheinungsjahr : | Juni 1975 |

| Ca. Neupreis : | 25 US $ |

| Taktfrequenz : | 20 KHz bis 2 MHz |

| Adreßbereich : | Maximal 16 Bit (65536 Byte) |

| Datenbusbreite : | 8 Bit |

| Befehle : | 56 |

| Adressierungsmodi : | 13 |

| Register : | - Akkumulator, 8 Bit - X und Y : zwei Index Register, 8 Bit - Stapelzeiger, 8 Bit - Prozessorstatus-Register, 8 Bit - Befehlszähler, 16 Bit |

| Stromaufnahme : | 5 V |

| Anzahl Pins : | 28 bis 40, je nach Modell |

| Gehäuseform : | DIP (Dual Inline Package) |

| Transistoren : | 3.510 |

| Strukturgröße : | 8.000 nm (21 mm²) |